![]()

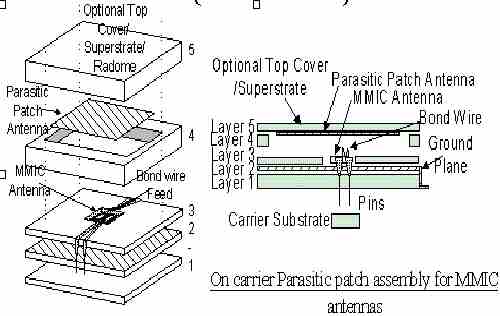

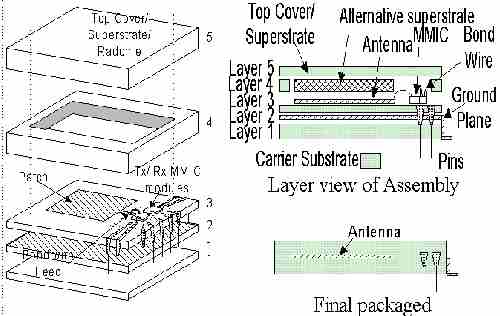

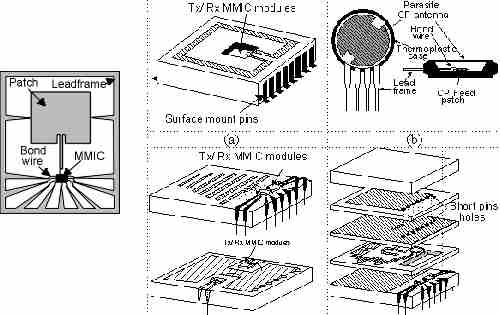

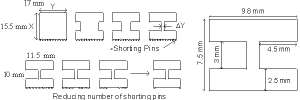

This is a novel method of achieving a complete RF front end product equipped with its radiator within a single chip package. It opens up the opportunity for the designs to be fully integrated in a silicon chip, hence keeping PCB board complexity to the minimum.

This packaging technique provides an alternative solution to problems associated with reduced size antennas implemented on Gallium Arsenide (GaAs) substrates; such as restoration of the antenna gain. This configuration will help to reduce manufacturing cost associated to connecting the antenna with the RF front-end chip. In principle, only the baseband signal, power supply and ground should be needed for such a configuration.

NOTE: This is a patent pending solution

..... small is beautiful.....

3. "Antenna design for packaged integrated R.F. front ends", IEE colloqium on Integrated small antenna for asset tracking, accepted.